# Make the Most Out of Last Level Cache in Intel Processors

**Alireza Farshin<sup>+</sup>, Amir Roozbeh**<sup>+\*</sup>, Gerald Q. Maguire Jr.<sup>+</sup>, Dejan Kostic<sup>+</sup>

**KTH Royal Institute of Technology (EECS/COM)**

**\*** Ericsson Research

farshin@kth.se amirrsk@kth.se maguire@kth.se dmk@kth.se

$\square$

## Problem

Faster links exposes processing elements to packets at a higher rate, but the performance of the processors is no longer doubling at the earlier rate, making it harder to keep up with the growth in link speeds. For instance, a server receiving 64 B packets at a rate of 100 Gbps has only **5.12ns** to process a packet before the next packet arrives.

## Slice-aware Memory Management

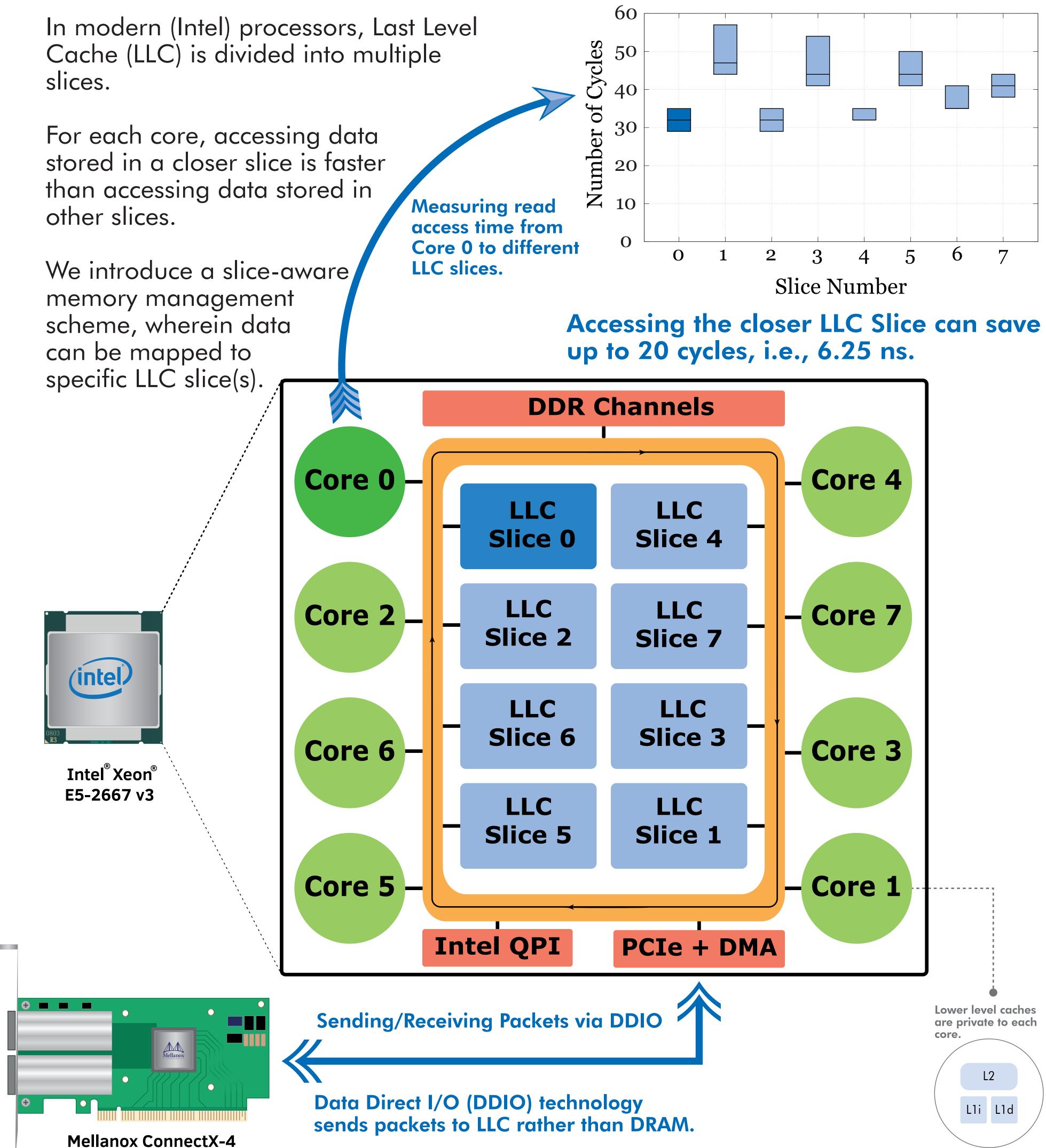

In modern (Intel) processors, Last Level Cache (LLC) is divided into multiple slices.

For each core, accessing data

#### **Approach:**

It is essential to exploit every oppurtunity to optimize current computer systems. We focus on better management of LLC.

CacheDirector 3

CacheDirector is a network I/O solution that extends DDIO by implementating slice-aware memory management as an extension to Data Plane Development Kit (DPDK).

It sends the first 64 B of a packet (containing the packet's header) directly to the appropriate LLC slice.

The CPU core that is responsible for processing a packet can access the packet header in fewer CPU cycles.

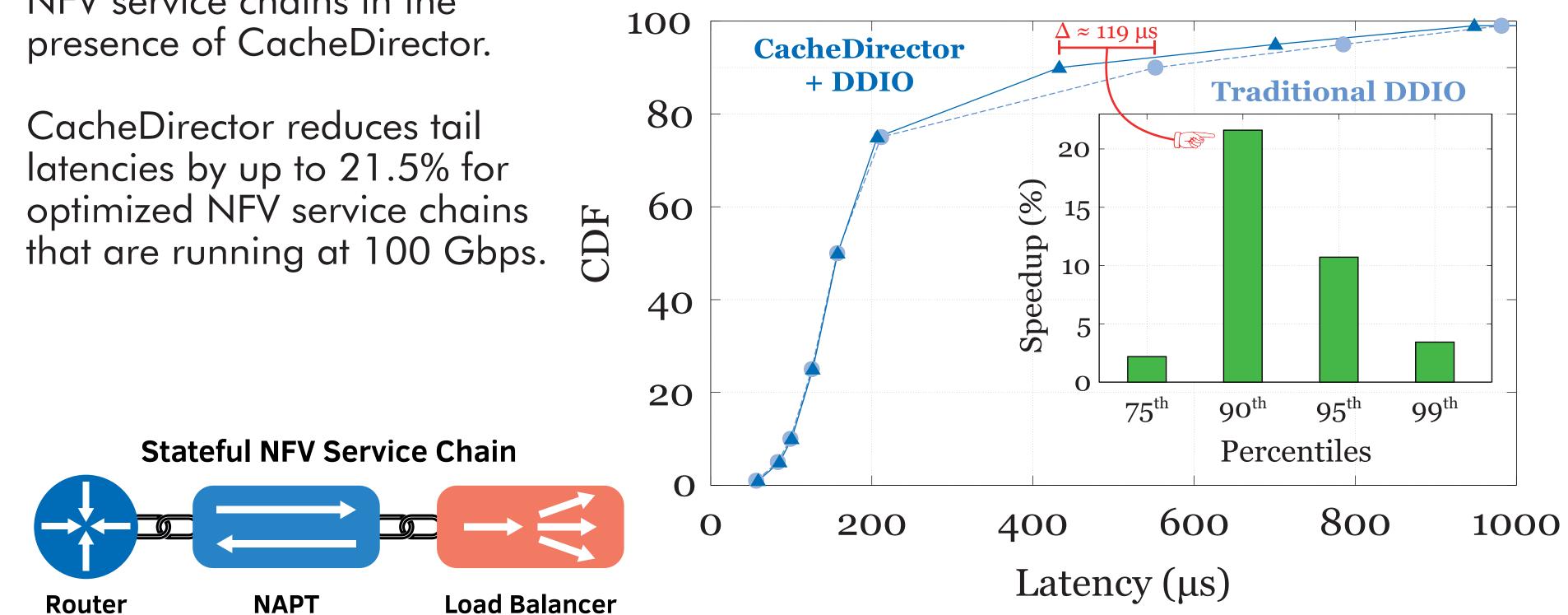

## Impact on Tail Latency for NFV Service Chains

#### Conclusions 5

We evaluate the performance of NFV service chains in the presence of CacheDirector.

CacheDirector reduces tail

With slice-aware memory management scheme, which exploits the latency differences in accessing different LLC slices, it is possible to boost application performance and realize cache isolation.

We proposed CacheDirector, a network I/O solution, which utilizes slice-aware memory management.

CacheDirector increases efficiency and performance, while reducing 🔎 Our Paper tail latencies over the state-of-the-art.

Work supported by SSF, WASP, and ERC.